# Design and Development of Entrenched Runtime Reconfigurable Nodule by Fault Tolerant Request

S. Ravichandran

Computer Science Department, Annai Fathima College of Arts & Science, Madurai, Tamil Nadu, India. drravichandran6@gmail.com

#### ABSTRACT

The need of the deficiency lenient application in a reconfigurable equipment improves the presentation of the runtime reconfigurable climate. Additionally the validated reconfiguration framework will guarantee more got and an exceptional framework .also the utilization of reconfigurable gadget grants far off and runtime HW design with got character and issue enduring application which suggests benefits in WSN sending, viability, security lastly cost decrease. In that article, WSN hub runtime reconfigurable remains handled as of a few viewpoints. In the first place, the sensor hub incorporates a business reconfigurable gadget, is called Field Programmable Gate Array (FPGA) these grants toward exploit this devices besides backing given in this business, although abusing that characteristic equipment parallelism respectively. In second, dual programming (SW) then equipment reconfigurable toward that WSN node, an entire runtime reconfigurable framework be affected by been characterized then intended pro that FPGA remembered for this bulge sequentially. In fourth likewise with complete runtime reconfigurable framework with deficiency lenient application additionally included by testing the hub by infusing the issue that may happen in the runtime.

Index Terms – General Purpose Processors (GPPs), ISE, Reconfigurable Architecture, UART, Wireless Sensor Networks (WSN), Micro Controller (MC), FPGA.

#### 1. INTRODUCTION

This arising innovation for Wireless Sensor Network (WSN) has altered this method inside whichever personalities associate by this actual sphere respectively. The WSN constructs bunch interdisciplinary exploration topics upon data managing, switch, communication and computation separately. The situation has similarly assumed innovative worldview toward manufacturing capability mechanization this strikingly imitates regulator, subsequent, checking, and diagnostics of that collecting measures then equipment [2] sequentially. This Wireless Sensor Networks (WSNs) address quite possibly that maximum difficult regions inside that present electronic industry [2], [3].

These organizations are required to be self-sufficient, low-power requesting, setting mindful, and adaptable. A last request can have hundreds for a huge number of device hubs supper out inside a climate, preparing this arrangement then that help for WSNs an impenetrable assignment. Albeit that combination innovations remain plainly having a tendency to brilliant sensor, there is as yet an expanding assortment of devices respectively. This boundaries then information handling needed pro devices switch are totally distinctive starting with single device then onto the next, yet in addition starting with one application then onto the next. In such setting, the utilization of indistinguishable hubs or a decreased arrangement of hubs that are additionally adjusted or potentially tweaked would improve on the sending cycle and lessen the item cost. Exemplary plan methodologies pro WSNs hub depend upon that utilization for the microcontroller (MC) [4], [5]. Nonetheless, preparing and usefulness needs are consistently expanding because of new application necessities and this incorporates WSNs requests respectively.

In that, additional toward this continually expanding heaviness pro decreasing opportunity toward-advertise, produces prompted new plan options, like reconfigurable equipment (HW).Reconfigurable frameworks have been concentrated somewhat recently by way of a choice pro together: Appliance- Specialized Integrated Circuits (ASICs) then General Persistence Palmtops (GPPs) respectively. The GPPs, pro example, endure a lopsidedness between IO (gadget Input-Outputs) and preparing. In an unexpected way, FPGAs give a lot of IOs, yet in addition high preparing because of the offered acquired for pipelining then parallelism sequentially. Moreover, reconfigurable frameworks give great adaptability by way of these may be refreshed afterward framework sending then furthermore grant period toward advertise decrease, meanwhile that legitimate model may be that last gadget. Subsequently, reconfigurable gadgets are continually acquiring piece of the pie and broadening their industry application areas and examination interest [6], [7]. For example, the work introduced in [8] centers around the utilization of FPGAs in industry control frameworks.

# 2. RELATED WORK

This Framework has, considerably more, presently, it is feasible to execute neural organizations and fluffy control arrangements on FPGAs [9] and furthermore, reconfigurable processing has been broadly investigated in speeding up applications, similar to computations identified with sub-atomic elements in [10]. In that article remains centered upon this utilization for reconfigurable frameworks inside WSNs respectively. A few exploration bunches have effectively abused the advantages of HW parallelism by planning impromptu reconfigurable gadgets arranged to be adjusted to a bunch of pre-recorded applications, as in [11] and [12]. The adaptability accomplished by that methodology is greater contrasted with ASIC-constructed arrangements, however not so great similarly so by little scrap reconfigurable gadgets, as FPGAs sequentially. Likewise, custom arrangements remain an additional limited as that need explicit Computer Aided Design (CAD) devices. In an unexpected way, this paper abuses industry accessible reconfigurable gadgets searching for high versatility and adaptability using the halfway runtime reconfiguration procedure, while exploiting the merchant gave CAD apparatuses.

Specifically, that article expects toward investigate then assess this utilization for fractional runtime reconfiguration inside WSNs, theme this has not been investigated inside that best in class. Runtime reconfiguration is a high level theme inside the reconfigurable figuring region, wherever modifications hooked on this FPGA setup are completed by runtime, whereas this gadget input and outputs then outstanding rationale remains reserved dynamic respectively. In this incredible component (just remembered for Atmel and Xilinx FPGAs) licenses not exclusively toward achieve HW refreshes on runtime then at whenever, yet in addition toward protect reminiscence planetary then encoding period contrasted with complete FPGA reconfiguration separately. Incomplete reconfiguration consumes effectively been abused in the auto business [13] and fit as a fiddle versatile video applications [14], where diverse reconfiguration systems are contemplated. Runtime reconfiguration will be tried inside a HW stage pro WSNs created on CEI, named Cookies then primary introduced inside [15] respectively.

This stage remains outlined inside this article, alongside a diagram of the WSNs best in class, to feature its distinctive attributes. This paper depicts the whole reconfigurable framework plan that incorporates: the meaning of the hub re-configurability situations, the help SW description then execution then, the natty gritty portrayal for that incomplete runtime reconfigurable framework description then configuration measure. To test the planned framework, a work process, likewise depicted in this paper, has been utilized to produce hub HW arrangements. Moreover, a bunch of common boundaries have been characterized toward assess this framework reconfiguration price then functional toward that objective hub. At long last, a fractional runtime reconfiguration usage instance has been made toward approve this plausibility of far off runtime reconfiguration inside WSNs respectively. This remainder of that article is coordinated by way of shadows. It incorporates the survey of the accessible mechanical and scholastic WSN alongside the concise portrayal of the Cookie measured hub engineering. The distinguished hub reconfiguration situations, alongside an overall perspective on a reconfiguration control middleware, are incorporated. This article gives this plan for that intended halfway runtime reconfiguration framework pro WSN then this total reconfiguration work process separately. This framework assessment dependent on broad reconfiguration price boundaries and this outcomes may be discovered inside Segment 5 respectively. The conversation of particular reconfigurable framework angles identified with WSN hubs can be found in this paper. At long last, ends are remembered for Segment 7 respectively.

## 3. PROBLEM STATEMENT

3.1 Cookie Device Bulge

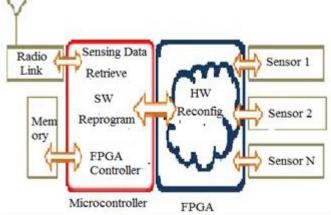

Figure 1 Diagram for Reconfigurable Node Design

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 9, Issue 5, May (2021)

This WSN hub where reconfiguration undertakings remain completed is the Cookie [7] respectively. In that hub come about planned considering a fundamental way of thinking: measured quality. Seclusion permits isolating and typifying the functionalities remembered for the hub. Subsequently, future updates may include just piece of the stage, which is attractive thinking about an opportunity to advertise. Besides, investigating utilizing this stage turns open, because of the hub adaptability, which makes conceivable the confirmation of a few ideas limiting the exertion separately. This Cookie survives made out for 4 principle stratums (additional stratums be able to be included upcoming renditions): handling, correspondence, control resource then devices respectively. Each stratum completes a particular errand, then that typifies this usefulness.

Then again, signals from computerized sensors are associated with the FPGA. On a fundamental level, the FPGA does all the handling identified with computerized sensors, to deliver the uC, which deal with the correspondences and cycles simple sensors. These days, there are a heap of sensors in the market with a few unique interfaces to convey their estimations. Large numbers of them incorporate computerized interfaces, with various conventions as SPI, I2C, 1-Wire, and so forth:

## 3.2 HW SW Reconfiguration

In this paper, hub re-configurability is related not just with stacking new SW programs in the microcontroller (SW reinventing), yet in addition new HW designs in the reconfigurable texture (HW reconfiguration). Identified with this, two general reconfiguration situations have been separated and applied to the Cookie hub. The first covers reconfiguration at network level that is generally needed during organization, where the last capacity of each organization hub is characterized (this incorporates the pre-owned sensors and information handling) or, when the organization work is changed (like in a crisis circumstance). The subsequent situation, reconfigurable coprocessor where calculation serious errands exploit the HW parallelism to ease up the microcontroller, as in [10]. The microcontroller is the center component in the hub re-configurability control. It is accountable for getting new HW designs and SW programs, oversee them and manage the FPGA reconfiguration. Maybe than stretching out a working framework to help re-configurability, as in [16] and [17], the objective inside this work has been to keep the framework as straightforward as could be expected.

#### 4. IMPLEMENTATION

## 4.1 Runtime Partial Re-configuration

The far off reconfigurable framework schematic view is appeared in "Fig. 1". The far off reconfiguration issue in the Cookie stage presents two viewpoints to be covered: Microcontroller reconstructing and FPGA reconfiguration.

## 4.1.1 Microcontroller Programming

The uC remembered for the Cookie (ADuC841 from Analog Devices) is modified utilizing its UART port. The uC remembers a sequential convention for request to have the option to program the uC through a host (I. e. a PC or other processor). Then again, the ZigBee module is associated with the uC sequential port. The uC sends orders to the ZigBee module to deal with the interchanges and sends the crude information to be conveyed to the organization. To reinvent the uC utilizing the remote ZigBee interface a supervisor program (called Cookie Manager) has been created. This supervisor completes every one of the means identified with uC program downloading through the sequential port. As a matter of first importance, a ZigBee channel should be set up between the sink (network organizer) and the distant hub wherein the reconstructing must be finished. Then, Cookie Manager sends every one of the orders expected to program the distant uC as though a genuine sequential link was associated between the host software engineer and the far off hub. At long last, the programming record is sent and is presented in the uC streak memory. The sequential downloading convention permits beginning code executing in the distant uC through a particular order. A program as well as other information can be stacked into the uC streak memory. So a common document downloaded to the uC to arrange the FPGA incorporates a program that goes about as a JTAG regulator and a record which incorporates the digit stream to be stacked into the FPGA with the directions that the JTAG regulator needs to execute to do the reconfiguration.

## 4.1.2 FPGA Programming

As to FPGA reconfiguration, the chose Spartan 3 doesn't have an inner setup port (ICAP), in this manner the leftover arrangement port choices are: Select Map and JTAG. As it has been now referenced, JTAG is the chosen reconfiguration interface. A SW execution of the JTAG regulator, given by Xilinx, has been utilized [12]. Hence no extra FPGA region is needed for the reconfiguration cycle control, as for example if Select Map was chosen, as in [10]. Then again, the fundamental disservice of utilizing JTAG is the reconfiguration time (JTAG is sequential, while Select Map equal).

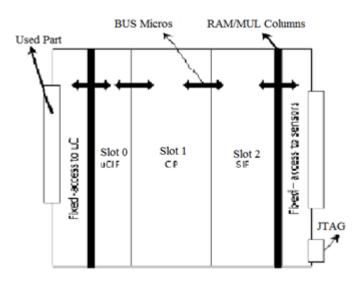

Figure 2 Diagram for Sensor Node Spartan 3 FPGA Virtual Architecture (VA)-Schematic View

The JTAG arrangement program running on the uC utilizes Xilinx explicit Boundary Scan design records (.xsvf) where the setup information is organized in double orders. In the current paper, just halfway bit streams are stacked into the FPGA, exploiting the fractional reconfiguration capacities of the Xilinx Spartan 3 FPGA. The VA is composed of three slots with different width and a pipeline like on-chip communication build by three types of bus macros.

To retarget the framework to other FPGAs (non-Xilinx) that can be customized by JTAG, a Xilinx device called svf2xsvf [11] can be utilized to change a limit filter standard ASCII record to a Xilinx twofold document. When the FPGA has been arranged by the uC, the last code for the application is downloaded into the uC streak memory. This progression is done similarly as it was clarified previously. Every one of these undertakings can be done between any two Cookies, abusing the multichip abilities of the ZigBee standard. This permits reconfiguring each hub associated with the organization with the lone disadvantage of time delay. Tests have been accomplished for a two jump arrangement as a proof of idea. When all the past VA plan contemplations have been set up, the FPGA VA is characterized by a bunch of records that outcome from the plan cycle: I) a client requirement document (.ucf document) that chiefly characterizes spaces positions and limits and ii) the communication macros used to fabricate the on-chip interchanges, that are given as generally positioned macros (.nmc documents).

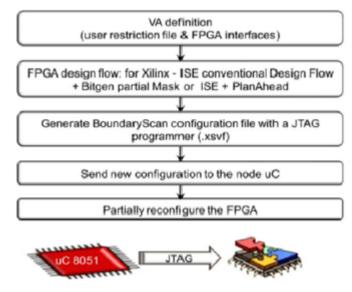

When the VA to be utilized has been chosen (a few VAs can be characterized for a solitary FPGA) and the connected definition records distinguished, hard centers for the objective framework can be planned. This interaction should be possible with an assortment of configuration streams, contingent upon the FPGA supplier. For Xilinx, one alternative is to utilize the customary ISE (Integrated System Environment) plan stream, given by Xilinx. This stream closes with the age of a full plan net rundown, from which hard centers are created utilizing bitten (the Xilinx device for bit stream age) by applying explicit incomplete veil choices. The subsequent methodology is to utilize the Xilinx incomplete reconfiguration configuration stream that depends on ISE and the Plan Ahead apparatus (appropriate for testing distinctive floor arranging draws near). Uniquely in contrast to the principal approach, the subsequent one straightforwardly delivers incomplete setup documents and has better steering by and large. For the in-your-face plan of the engineering introduced in this paper, the main methodology was chosen as it allows the utilization of for nothing adaptation of the device (ISE web pack) and in light of the fact that the floor planning in our plan technique is as of now remembered for the VA definition.

The rundown of the right now accessible centers are the accompanying:-

\* Coprocessors (CP): An eight pieces moving normal channel that continually gathers estimated information and gives a normal worth, and a FIR channel Coprocessors (CP): An eight pieces moving normal channel that continually gathers estimated information and gives a normal worth, and a FIR channel

\* Microcontroller Interface (uCIF): There is one adaptation for getting to advanced sensors information (uCDIF)

\* Sensor interface (SIF): There are hard centers accessible for the temperature and the accelerometer sensors in two variants: I) one utilizing the inserted multipliers (MULs) accessible in the BRAM/MUL segment that relate to opening 2, and ii) a second form that carries out the augmentations in LUTs Sensor interface (SIF): There are hard centers accessible for the temperature and the

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 9, Issue 5, May (2021)

accelerometer sensors in two variants: I) one utilizing the inserted multipliers (MULs) accessible in the BRAM/MUL segment that relate to opening 2, and ii) a second form that carries out the augmentations in LUTs.

Figure 3 Diagram for Runtime ESN Node Partial Reconfiguration Working Flow Design

The total work process used to test halfway reconfiguration in WSNs is introduced in Fig. 3. As it very well may be seen, the stream begins with a virtual engineering choice and afterward proceeds with the all-around depicted in-your-face plan. From that point forward, autonomously from the technique used to create fractional design records, the following stage is to utilize a JTAG FPGA programming device (iMPACT for Xilinx FPGAs) to produce the necessary paired organized limit examine setup document. From that point forward, the following stage of the work process is to send new arrangements through the organization to an objective hub, where they are saved in a nearby memory and halfway reconfiguration is performed.

## 4.2 Fault Injection and Testing

A test design has been created to test the given contribution from the microcontroller. It incorporates aADCinput/yield lock for the yield response analyzer. The analyzer will test the info design and create a yield if the tried example is issue. On the off chance that a deficiency is created again the example is tried for the reconfiguration design. In any case the yield is sent to the yielded network for shrewd transmission network Automatic Test Pattern Generation (ATPG): Automatic test design age is calculation that infuses a shortcoming into a circuit, and afterward utilizes an assortment of components to actuate the flaws and cause its impact to proliferate through the equipment and show itself at a circuit yield. The yield signal changes from the worth expected for the issue free circuit and this makes the issue be distinguished.

## 4.2.1 Output Response Analyzer (ORA)

Output Response Analyzer is utilized to contrast the got yield and reference yield. Assuming the acquired yield coordinates with the reference yield, the ORA sends it to Micro regulator, on the off chance that it doesn't matches the reference yield, it sends it again to CUT for additional interaction. These are the activity occurred in the Circuit under Test. The trustworthiness assessment of complex issue open minded frameworks requires a mix of both test and scientific techniques.

## 4.3 Authenticated Reconfiguration

This paper proposed with the got reconfiguration philosophy over any client can ready to get to the reconfigurable hub easily. Communicating the bit stream must be done in a protected way to keep an assailant from perusing or adjusting the bit stream. We propose an arrangement wherein the FPGA is the single gadget in the system's zone-of-trust. The outcome is a FPGA design that is separated into a static and a powerful district. The static locale holds the correspondence, security and recon<sup>-</sup> gyrations facilities, while the powerful area contains the focused on application. The distinction with our answer is that we expect the FPGA to be the solitary gadget inside the framework's zone-of-trust. Further, our engineering permits a simple development of the cryptographic usefulness. From these set up we can accomplish.

- \* congeniality of the bit stream

- \* 2Authenticity of the bit stream

- \* Authenticity of the focal reconfiguration unit and the FPGA

- \* Expendability of the cryptographic functionalities

To characterize an application on top of a fractional runtime reconfigurable framework, the initial step (before any halfway reconfiguration) is to play out a FPGA full design. In the methodology continued in this paper, the main FPGA design is utilized to stack the virtual engineering definition, that is, to hold opening regions and to stack the on-chip correspondence assets. This arrangement is kept in the FPGA boot-stacking memory, in a different gadget from where the setup is perused on power up (in the new Spartan3AN FPGA this memory is installed in the silicon die). In the underlying design, feed through setups are stacked in space 0 and opening 1, while opening 2 is left vacant. After this, any application can be organized on the FPGA.

## 5. IMITATION OUTCOMES

The figure shows the fractional reconfiguration of a hub with various piece rate and examining time resolution. The hub can be arranged at an ideal channel. The figure shows the shortcoming lenient utilization of the detecting hub with the test design generation. Whether the arrangement of touch is communicated over the circuit under test and contrasted and the test design successions and confirmed with yield signal.

Figure 4 Reconfiguration of Three Sensor Node

Figure 5 Fault Injection and Correction

#### 6. CONCLUSION

The work introduced in this paper is a way to deal with open new skylines to the utilization and improvement of runtime reconfigurable Wireless Sensor Networks. The work shows the practicality of the reconciliation of new reconfiguration strategies in WSN that may prompt change the utilization of WSNs, from specially crafted for an offered application, to nonexclusive organizations arrangements where errands and capacities are powerfully apportioned. The considered updates cover both runtime HW reconfiguration and SW refreshes, and included with new functionalities of deficiency enduring application, refreshing of safety data, the combination of reconfigurable in WSN hubs may bring about lightening some expensive exercises in the mechanical utilization of WSNs, similar to arrangement and support.

#### REFERENCES

- [1] Yana EstevesKrasteva, Jorge Portilla, Eduardo de la Torre, and Teresa Riesgo"Embedded Runtime econfigurable Nodes forWireless Sensor Networks Applications" in IEEE sensors journal, vol. 11, no. 9, september 2011.

- [2] L. Q. Zhuang, K. M. Goh, and J. B. Zhang, "The wireless sensor networks for factory automation: Issues and challenges," in Proc. IEEE Conf. Emerging Technol. Factory Autom., ETFA'07, Sep. 25–28, 2007, pp. 141–148.

- [3] A. Willig, "Recent and emerging topics in wireless industrial communications: A selection," IEEE Trans. Ind. Informat., vol. 4, no. 2, pp. 02–124, May 2008.

- [4] J. Polastre, R. Szewczyk, and D. Culler, "Telos: Enabling ultra- low power wireless research," in Proc. 4th Int. Symp. Information Sensor Networks, IPSN'05, Apr. 2005, pp. 364–69.

- [5] S. Yamashita, T. Shimura, K. Aiki, K. Ara, Y. Ogata, T. Tanaka, H. Kuriyama, K. Shimada, and K. Yano, "A 15 4, reliable sensor-net module: Enabling application-specific nodes," in Proc. 5th IEEE/ACM Int. Conf. Inform. Process. Sensor Networks, IPSN'06, Apr. 2006, pp. 383–390

- [6] J. J. Rodrigez-Andina, M. J. Moure, and M. D. Valdes, "Features, design tools, and application domain of FPGAs," IEEE Trans. Ind.Electron., vol. 54, no. 4, pp. 1810–1823, Aug.2007

- [7] W. H. Mangione-Smith et al., "Seeking solutions in configurable computing," IEEE Computer, vol. 30, no. 12, pp. 38-43, Dec. 1997

- [8] R. Scrofano, M. B. Gokhale, F. Trouw, V. K. E.Monmasson, and M. N. Cirstea, "FPGA design methodology for industrial control systems—A review," IEEE Trans. Ind. Electron., vol. 54, no. 4, pp. 1824–1842, Aug. 2007.

- [9] H. Chaoui, M. C. E. Yagoub, and P. Sicard, "FPGA implementation of a fuzzy controller for neural network based adaptive control of a flexible joint with hard nonlinearities," in Proc. IEEE Int. Symp. Ind. Electron. Jul. 2006, vol. 4, pp. 3124–3129.

- [10] R. Scrofano, M. B. Gokhale, F. Trouw, and V. K. Prasanna, "Accelerating molecular dynamics simulations with reconfigurable computers," IEEE Trans. Parallel and Distrib. Syst., vol. 19, no. 6, pp. 764–778, Jun. 2008.

- [11] H. Hinkelmann, P. Zipf, and M. Glesner, "Design concepts for a dynamically reconfigurable wireless sensor node," in Proc. 1<sup>st</sup> NASA/ESA Conf. Adaptive Hardware and Systems, AHS'06, Jun. 2006, pp. 436–441.

- [12] A. E. Susu, M. Magno, A. Acquaviva, and D. Atienza, "Reconfiguration strategies for environmentally powered devices: Theoretical analysis and experimental validation," Trans. HiPEAC I, LNCS 4050, pp. 341–360, 2007

- [13] J. Becker et al., "Dynamic and partial FPGA exploitation," Proc. IEEE, vol. 92, no. 2, pp. 438-452, Feb. 2007.

- [14] P. Sedcole, Y. K. Peter, C. George, A. Constantinides, and W. Luk, "Run-time integration of reconfigurable video processing systems," IEEE Trans. VLSI Syst., vol. 15, no. 9, pp. 1003–1016, Sep. 2007

- [15] J. Portilla, A. de Castro, E. de la Torre, and T. Riesgo, "A modular architecture for nodes in wireless sensor networks," J. Univ. Comput.Sci. (JUCS), vol. 12, no. 3, pp. 328–339, Mar.2006

- [16] Portilla, J. L. Buron, A. de Castro, and T. Riesgo, "A hardware library for sensors/actuators interfaces in sensor networks," in Proc. IEEE Int.Conf. Electron., Circuits and Systems 2006 (ICECS'06), Niza, France, Dec. 2006, pp. 1244–1247

- [17] C. Steiger, H. Walder, and M. Platzner, "Operating systems for reconfigurable embedded platforms: Online scheduling of real- time tasks," IEEE Trans. Comput., vol. 53, no. 11, pp. 1393–1407, Nov. 2004.

Author

**Dr. S. Ravichandran**, M.C.A., M.Phil. M.Tech., ME., Ph.D., working as a HOD & Professor in Department of Computer Science at Annai Fathima College of Arts & Science, Madurai, Tamilnadu State, India. He has 23 years of teaching experiences in various Colleges. He has Published 29 papers in International journals, he has presented in 17 International Conferences & presented in 19 National Conferences at various Engineering Colleges. His areas of specialization are Cloud Computing, Artificial Intelligence, Networks, software engineering and Compilers.